Próba budowy prostego roszrzenia na clockport - podejście trzecie

Opis

Tym razem przynajmniej wydaje mi się, że wiem co robię.

08.01.2013 10:47

[#1]

Re: Próba budowy prostego roszrzenia na clockport - podejście trzecie

Cokolwiek to jest to trzymam kciuki za powodzenie tego projektu!

08.01.2013 14:03

[#2]

Re: Próba budowy prostego roszrzenia na clockport - podejście trzecie

@Skiba, post #1

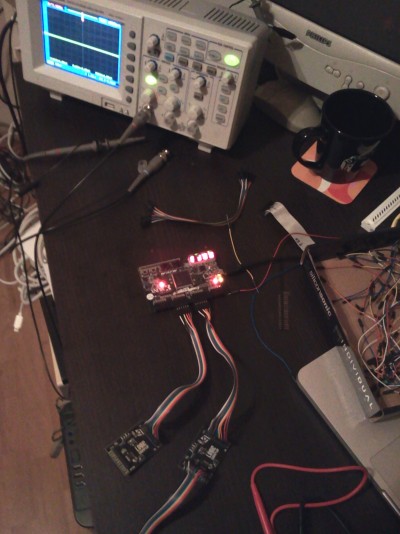

Póki co to tylko jest płytka z CPLD, z zaimplementowanymi kilkoma rejestrami, którymi mogę sterować po USB z kompa z Linuxem. Teraz pracuję nad podłączeniem tego "z drugiej strony" do clockportu (poprzez dwa widoczne na zdjęciu konwertery poziomów logicznych - Amiga ma 5V, płytka CPLD na portach GPIO 3.3V).

08.01.2013 23:10

[#6]

Re: Próba budowy prostego roszrzenia na clockport - podejście trzecie

@rafgc, post #5

Podejście drugie to był PIC, więc je znasz  . Niestety okazało się nieco zbyt skomplikowane jak na moje umiejętności programowania niskopoziomowego. Właściwie problemem była synchronizacja wbuowanego ethernetu z clockportem, więc na obecną chwilę mam ochotę zaimplementować w CPLD (VHDL) bardzo prosty interfejs komunikacji USB-Amiga. Jak napisałem wyżej, komunikację USB-CPLD mam w zasadzie opanowaną. Tzn. potrafię sterować już wbudowanymi w płytkę prototypową elementami, oraz tworzyć własne rejestry dostępne po USB. Teraz kwestia sprzęgnięcia tego z clockportem. Póki co próbowałem zaimplementować prosty model behavioral który by zczytywał bity z szyny adresowej clockportu i wyświetlał ostatni użyty rejestr na wyświetlaczu 7-segmentowym. Póki co mam dziwne problemy z timinagami, które pewnie wynikają z mojej niewiedzy w temacie.

. Niestety okazało się nieco zbyt skomplikowane jak na moje umiejętności programowania niskopoziomowego. Właściwie problemem była synchronizacja wbuowanego ethernetu z clockportem, więc na obecną chwilę mam ochotę zaimplementować w CPLD (VHDL) bardzo prosty interfejs komunikacji USB-Amiga. Jak napisałem wyżej, komunikację USB-CPLD mam w zasadzie opanowaną. Tzn. potrafię sterować już wbudowanymi w płytkę prototypową elementami, oraz tworzyć własne rejestry dostępne po USB. Teraz kwestia sprzęgnięcia tego z clockportem. Póki co próbowałem zaimplementować prosty model behavioral który by zczytywał bity z szyny adresowej clockportu i wyświetlał ostatni użyty rejestr na wyświetlaczu 7-segmentowym. Póki co mam dziwne problemy z timinagami, które pewnie wynikają z mojej niewiedzy w temacie.

09.01.2013 20:11

[#8]

Re: Próba budowy prostego roszrzenia na clockport - podejście trzecie

@rafgc, post #7

Na płytce jest mikrokontroler, jest dostępna biblioteka do komunikacji z nimi (na stronie producenta płytki). Kontroler jest podłączony prostą 8-bitową szyną do CPLD. Więc właściwie ja nie musiałem implementować nic związanego z USB, a jedynie komunikację z tym mikokontrolerem, który działa jako urządzenie USB podłączane do komputera.

09.01.2013 23:19

[#10]

Re: Próba budowy prostego roszrzenia na clockport - podejście trzecie

@strim, post #9

Różne wersje ISE będą generować różną konfigurację, czasami mogą to być jednak różnice jednej makroceli lub żadne, stopień optymalizacji kompilacji pod kątem szybkości lub zasobów też może mieć znaczenie. Sam specjelnie kodu nie zoptymalizujesz, możesz się posłużyć jakimś poradnikiem np. http://www.xilinx.com/support/documentation/application_notes/xapp444.pdf, ale nie zawsze idzie cokolwiek zoptymalizować. Ilość wykorzystanych makroceli zależy od konstrukcji PLD, taka makrocela ma np jakąś określoną ilość wejśc i np jedno wyjście (więc może realizować tylko jeden cel , tak zdaje się jest w xilinxie w typowym PLD), użycie np jednego bitu na rejestr może więc skutkować zużyciem jednej makroceli. Niektóre nowsze PLD mają strukturę podobną do FPGA i tam to już jest troszkę inaczej.