05.03.2025 19:40

[#61]

Re: A640

@Dorian3d, post #60

Dorian nie pisałem po co 040, tylko, że jest alternatywa dla tych co chcą "szybciej szybciej". Tak jak ty mam kilka turbosów 060 i 040. Trzeba być tylko świadomym ich ograniczeń.

Narzekać, że gry 3D nie działają dostatecznie szybko na 68k i mówić, że postorm jest be. Coś za coś.

Z 040 może można tak jak w 060 przyspieszyć przez emulacje L2 cache w pamieci DDR? Taką sztuczkę wykorzystuje Warp1260, ale A640 chyna nie ma DDR?

Narzekać, że gry 3D nie działają dostatecznie szybko na 68k i mówić, że postorm jest be. Coś za coś.

Z 040 może można tak jak w 060 przyspieszyć przez emulacje L2 cache w pamieci DDR? Taką sztuczkę wykorzystuje Warp1260, ale A640 chyna nie ma DDR?

06.03.2025 22:56

[#64]

Re: A640

@snifferman, post #61

Czemu nazywasz zewnętrzną pamięć CACHE emulacją? :) SDR wymagałby podwójnego taktowania, żeby osiągnąć to samo, co przy 060 i 100MHz szybko staje się zaporą (166MHz to chyba max w popularnych kostkach SDR), do tego zapewne należałoby użyć FPGA, który ma szybki wbudowany SRAM. CPLD go nie ma i z tego powodu nie nadaje się do takich celów, implementacja pamięci zżera zasoby jak szalona, jedna makrocela to 1bit, linia cache 030/040 to 16 bajtów/128bitów, a gdzie jeszcze logika tym zarządzająca, która potrzebuje jakichś tabeli i flag do zaznaczania, która strona pamięci jest w cache, która jest wolna, etc., czyli jeszcze więcej pamięci.

Chyba nie jest to takie trudne do sprawdzenia na prawdziwej karcie z 040, ile w teorii dałby poglądowo taki moduł, należałoby napisać test, który mieści się w 4kb, a potem zrobić to samo, tylko w rozwiniętej pętli albo wyłączyć cache'owanie dla obszaru w którym jest program testowy za pomocą MMU (może jakiś koder miałby lepszy pomysł na to).

Chyba nie jest to takie trudne do sprawdzenia na prawdziwej karcie z 040, ile w teorii dałby poglądowo taki moduł, należałoby napisać test, który mieści się w 4kb, a potem zrobić to samo, tylko w rozwiniętej pętli albo wyłączyć cache'owanie dla obszaru w którym jest program testowy za pomocą MMU (może jakiś koder miałby lepszy pomysł na to).

06.03.2025 23:47

[#65]

Re: A640

@bulbulator, post #64

Czemu nazywasz zewnętrzną pamięć CACHE emulacją?

Bo normalnie L2 był robiony na SRAM. DDR to pamięć innego typu. Trzymałem się definicji z wiki

"programowe symulowanie działania określonego oprogramowania lub platformy sprzętowej przez inny system lub na sprzęcie innego typu"

Jest też tylko wydzielony adresowo z pamięci fizycznej, która służy jako FAST. Takie rozwiązania też są na innych kartach dla pamięci SLOW. Ale to nie jest istotne i nie będę się spierać. Niech będzie, że to Cache innego typu bez emulacji. Istotne jest czy to daje duże przyspieszenie.

166MHz to chyba max w popularnych kostkach SDR

Widziałem 200Mhz (EM63A165TS-5G), ale z tego co pamiętam były droższe od 166Mhz i pewnie ekonomiczniej i wydajniej zrobić to na szybkich DDRach.

07.03.2025 01:48

[#66]

Re: A640

@snifferman, post #65

Bo normalnie L2 był robiony na SRAM. DDR to pamięć innego typu. Trzymałem się definicji z wiki

Ta definicja opisuje to trochę od d..y strony :) . Pamięć Cache to moduł Cache + pamięć, w której przechowuje on są ostatnio odczytane dane, jej typ nie ma znaczenia, akurat tak się złożyło po prostu, że pamięć SRAM była stosowana, bo była najszybsza. Co innego, gdybyś emulował samą kostkę SRAM za pomocą DDRAM, (P-SRAM jest czymś podobnym), ale wtedy dalej byś nie emulował CACHE, tylko interfejs pamięci dla modułu CACHE.

Widziałem 200Mhz (EM63A165TS-5G), ale z tego co pamiętam były droższe od 166Mhz i pewnie ekonomiczniej i wydajniej zrobić to na szybkich DDRach.

No raczej tak biorąc pod uwagę, że SDR to już wobec obecnych czasów archaizm i za daleko z taktowaniem nie polecisz.

Już samo taktowanie pamięci szybciej niż procesor da przyśpieszenie, bo pozwoli mu na odczyt danych wcześniej, niż gdyby procesor miał czekać np. 3 cykle na pojawienie się danych. Kopiowanie w pamięci by na tym zyskało oraz oprogramowanie, które nie zostało zoptymalizowane pod 040 i wywołuje dużo "cache miss" - wtedy czas dostępu poprawi sytuację. Trudno to oszacować dokładnie, bo dane oprogramowanie może być tak napisane, że moduł cache w żaden sposób nie będzie w stanie pomóc, np. przy rozwiniętych pętlach większych, niż sam cache. Nie zapomnijmy też o samym kontrolerze pamięci, który na samym SD-RAMie ma potencjał dać lepsze rezultaty niż na DRAM'ie i wtedy taki CACHE by zrobił mniejszą różnicę, może być w ogóle tak, że przy 25MHz taki moduł wcale by nie musiał być potrzebny, tak jak przy procesorach 020, gdzie przy 28MHz jeszcze dało radę zrobić kontroler pamięci, przy którym procesor pracował bez waitstate'ów i osiągał maksimum swoich możliwości przy danym taktowaniu.

Ostatnia aktualizacja: 07.03.2025 01:50:06 przez bulbulator

09.03.2025 00:09

[#70]

Re: A640

@ted, post #69

Ale PCB amigi nie ma przelotek na piny do CPU. Więc jak to miałoby działać? Turbo z pinami pod specjalne PCB Amigi 600 z pinami/złączem żeńskim? A jak ktoś ma oryginalną PCB A600, to musi zrobić przeszczep? A630, które mam nie ma zbytnio problemów z kontaktem. te podstawki użyte w turbo są dość mocne i możesz na niej podnieść całą Amigę i się nie wyczepi. Problemem mogą być zaśniedziałe piny CPU. Miałem właśnie jeden egzemplarz A600, gdzie A630 nie wstawało. Pomogło czyszczenie i przelutowanie procesora

10.03.2025 19:22

[#74]

Re: A640

@Bociek78, post #73

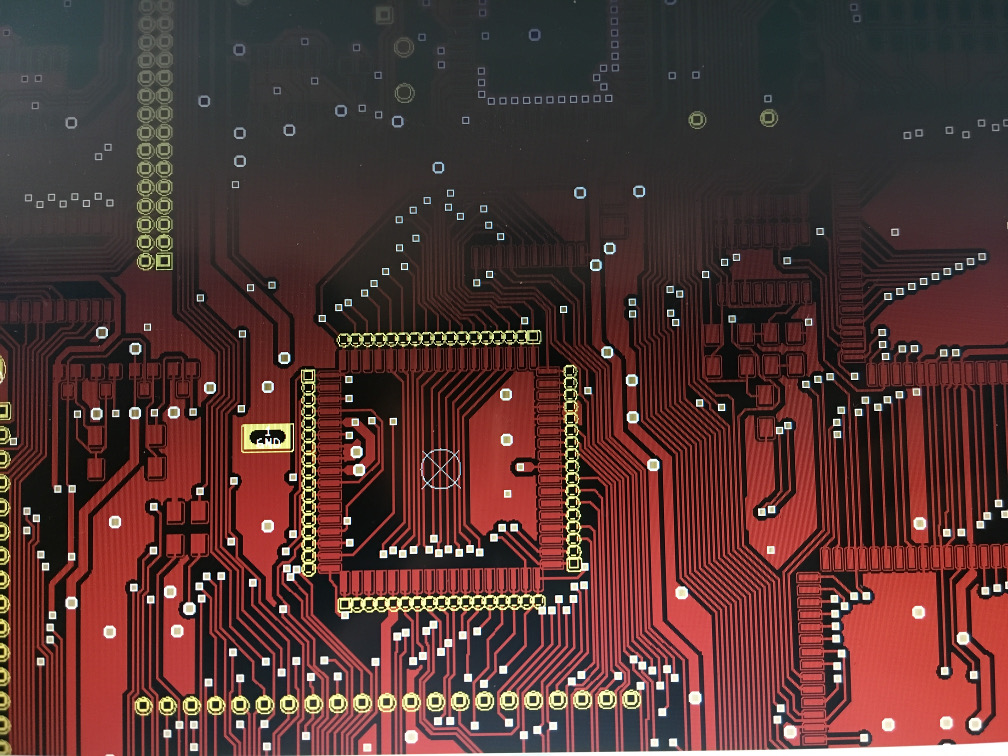

Weź se tego na czerwonej gąbce

@Dorian3D

Nie widzę żadnego w najnowszych maskach, dwa D50D i nieco nowsze E31F i E42K. No chyba że te na samej górze, ale fotka jest rozmazana.

Ja miałem tylko jednego LC040@33 w masce E71M, ale dałem go Paulinie.

Ostatnia aktualizacja: 10.03.2025 19:29:47 przez waldiamiga

@Dorian3D

Nie widzę żadnego w najnowszych maskach, dwa D50D i nieco nowsze E31F i E42K. No chyba że te na samej górze, ale fotka jest rozmazana.

Ja miałem tylko jednego LC040@33 w masce E71M, ale dałem go Paulinie.

Ostatnia aktualizacja: 10.03.2025 19:29:47 przez waldiamiga