13.09.2017 14:59

[#751]

Re: Protein turbo A500

@Adinfo, post #750

Ja dzisiaj będę swoją programować więc żebym niczego nie spierdzielił chciałbym potwierdzić info, którego nie mogę znaleźć w tym wielgachnym wątku a w instrukcji Jacka Swidnika niestety nie znalazłem:

1. czy pinout jtaga na proteinie jest następujący?

2. Jaka jest minimalna konfiguracja proteiny by sprawdzić czy działa? Wszystko rozwarte?

3. Jaki jest pinout w ZL11PRG v.2 bo nigdzie tego nie widzę?

Ostatnia aktualizacja: 13.09.2017 15:09:53 przez teh_KaiN

1. czy pinout jtaga na proteinie jest następujący?

5678 1234 1 - TCK 2,4,8 - GND 3 - TMS 5 - TDI 6 - VCC 7 - TDO

2. Jaka jest minimalna konfiguracja proteiny by sprawdzić czy działa? Wszystko rozwarte?

3. Jaki jest pinout w ZL11PRG v.2 bo nigdzie tego nie widzę?

Ostatnia aktualizacja: 13.09.2017 15:09:53 przez teh_KaiN

13.09.2017 15:18

[#753]

Re: Protein turbo A500

@Kilos, post #752

To jak w końcu z tym pinoutem, bo wg Twojego rysunku jest jak niżej i masa mi się bardzo nie zgadza:

A pinout programatora faktycznie jest w manualu, bo cwaniaczki mi wysłali tylko jego pierwszą stronę i zdurniałem. w PDFie w sklepie jest.

Ostatnia aktualizacja: 13.09.2017 15:20:03 przez teh_KaiN

5678 1234 1 - TCK 2 - TMS 3 - TDI 4 - TDO 5, 6, 8 - GND 7 - VCC

A pinout programatora faktycznie jest w manualu, bo cwaniaczki mi wysłali tylko jego pierwszą stronę i zdurniałem. w PDFie w sklepie jest.

Ostatnia aktualizacja: 13.09.2017 15:20:03 przez teh_KaiN

13.09.2017 18:32

[#755]

Re: Protein turbo A500

@Kilos, post #754

Czekajcie chwilę - zapodam zaraz jak ma być - wydaje mi się, że już to pisałem wcześniej.

Mam na stałe podpięty kabel z tego programatora (do momentu jak jeszcze działał).

W Protein jest zły opis, ma być tak:

W ZL11PRG v2:

Nie miałem podglądu przy edycji, mogło się rozjechać.

Ostatnia aktualizacja: 13.09.2017 18:50:52 przez Adinfo

Mam na stałe podpięty kabel z tego programatora (do momentu jak jeszcze działał).

W Protein jest zły opis, ma być tak:

GND GND VCC GND 2 4 6 8 1 3 5 7 TCK TMS TDI TDO

W ZL11PRG v2:

GND VCC ispEN RESET GND 2 4 6 8 10 1 3 5 7 9 SCLK SDOUT MODE NC SDIN

Nie miałem podglądu przy edycji, mogło się rozjechać.

Ostatnia aktualizacja: 13.09.2017 18:50:52 przez Adinfo

13.09.2017 18:58

[#756]

Re: Protein turbo A500

@Adinfo, post #755

Nie mogłem już edytować:

W Protein widok - SIMM na górze a JTAG na dole. W ZL11PRG jak by patrzyć na jego gniazdo (napisy model itd. na obudowie programatora z góry)

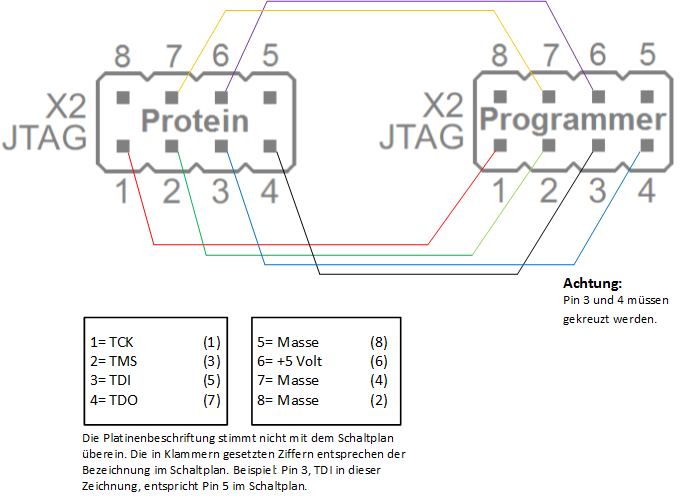

Protein / ZL11PRG V2

drobna uwaga: nie podpinać programatora pod LPT przy włączonym kompie, wyłączyć PC, podpiąć programator, podłączyć Protein pod zasilanie (lub programator pod zasilanie - wtedy z niego poleci zasilanie do Protein), dopiero wtedy włączyć kompa, mam wrażenie, że samodzielnie mogłem uwalić mój programator przez jakiś przeskok itp. ale teraz trudno mi do tego dojść. Albo miałem pecha bo nie kupiłem nowego.

Ostatnia aktualizacja: 13.09.2017 19:01:52 przez Adinfo

W Protein widok - SIMM na górze a JTAG na dole. W ZL11PRG jak by patrzyć na jego gniazdo (napisy model itd. na obudowie programatora z góry)

Protein / ZL11PRG V2

6 VCC | 4 VCC 8 GND | 2 GND 1 TCK | 1 SCLK 3 TMS | 5 TMS 5 TDI | 3 SDOUT 7 TDO | 9 SDIN

drobna uwaga: nie podpinać programatora pod LPT przy włączonym kompie, wyłączyć PC, podpiąć programator, podłączyć Protein pod zasilanie (lub programator pod zasilanie - wtedy z niego poleci zasilanie do Protein), dopiero wtedy włączyć kompa, mam wrażenie, że samodzielnie mogłem uwalić mój programator przez jakiś przeskok itp. ale teraz trudno mi do tego dojść. Albo miałem pecha bo nie kupiłem nowego.

Ostatnia aktualizacja: 13.09.2017 19:01:52 przez Adinfo

13.09.2017 19:43

[#758]

Re: Protein turbo A500

@Kilos, post #757

Załapałem  Jakoś nie popatrzyłem na Rys.4 z instrukcji tylko od początku sugerowałem się Rys.9. Pinout mam dobry tylko zły opis zapodałem

Jakoś nie popatrzyłem na Rys.4 z instrukcji tylko od początku sugerowałem się Rys.9. Pinout mam dobry tylko zły opis zapodałem

koniec mieszania:

Ostatnia aktualizacja: 13.09.2017 19:49:21 przez Adinfo

koniec mieszania:

6 VCC | 4 VCC 8 GND | 2 GND 1 TCK | 1 TCK 3 TMS | 5 TMS 5 TDI | 3 TDO 7 TDO | 9 TDI

Ostatnia aktualizacja: 13.09.2017 19:49:21 przez Adinfo

13.09.2017 20:49

[#759]

Re: Protein turbo A500

@Adinfo, post #758

No i problem, ale nie z programowaniem. Gdzieś na swojej proteinie mam zwarcie między +5V a GND. Myślałem że na SIMMie, bo pełno blobów z cyny mi tam powstało na pinach (dokładałem jej i dokładałem i dziwiłem czemu nie zostaje na polach lutowniczych a spływała w kierunku gniazda), ale wszystkie proteiny Toma Raina mają ten sam problem, więc robi się z tego 5 wadliwych PCB. Była to jedna z pierwszych partii organizowanych przez Lukzera, w kolorze czarnym. Oczywiście żadnych pretensji do nikogo nie mam, ale chciałbym ten problem rozwiązać. ;)

Ktoś miał podobny problem? Na koniec weekendu będę miał dostęp do jeszcze jednego pcb z tej serii i ją przegwizdam, ale może problem jest znany a tylko został przeze mnie przeoczony.

Ktoś miał podobny problem? Na koniec weekendu będę miał dostęp do jeszcze jednego pcb z tej serii i ją przegwizdam, ale może problem jest znany a tylko został przeze mnie przeoczony.

13.09.2017 23:09

[#762]

Re: Protein turbo A500

@teh_KaiN, post #761

Z portu USB to może być trochę mało prądu. Bez odpowiednich pull-up-ów na liniach danych USB nie da Ci więcej jak 500mA, a jak tyle da to i tak dobrze... Na czas programowania polecam podpiąć pod piny socketu CPU, zewnętrzne 5V. Możesz reż w piny jtag (vcc i gnd) sam programator, nie zasila PCB w czasie programowania.

14.09.2017 09:35

[#763]

Re: Protein turbo A500

@MariuszK, post #762

Podpinałem wcześniej zasilanie do podstawku CPU na Proteinie, VCC (14, 49) i GND (16, 53) występują w dwóch miejscach: po znalezieniu odpowiednich pinów oznaczyłem je od góry markerem: czarny GND, czerwony VCC (aby nic nie pomylić) i przez dolutowane do przelotki goldpiny włożyłem je w podstawkę CPU na Proteinie, stąd przez JTAG programator dostał napięcie zasilające.

Ostatnia aktualizacja: 14.09.2017 09:35:33 przez Adinfo

Ostatnia aktualizacja: 14.09.2017 09:35:33 przez Adinfo

14.09.2017 11:21

[#766]

Re: Protein turbo A500

@dragmar, post #765

Tych machów kupiłem 21 pod koniec 2016 roku. Trudno mi to teraz ocenić bo pierwsze 3 sztuki poszły bez błędów, a niedawno drugi komplet już coś nie grało - musiałem wyłączyć sprawdzanie błędów - ale ten drugi zestaw machów działa identycznie jak pierwszy.

Raczej mam wrażenie, że złe wsady wgrałem albo coś mam tak samo "źle" wlutowane" w każdym egzemplarzu.

Raczej mam wrażenie, że złe wsady wgrałem albo coś mam tak samo "źle" wlutowane" w każdym egzemplarzu.

16.09.2017 14:54

[#768]

Re: Protein turbo A500

@Kilos, post #70

Dzięki Kilos za post #70

Kupiłem programator ZL4PRG - będę ciąć kilka ścieżek, parę połączeń trzeba będzie dorobić, wymienić kilka rezystorów i kondensatorów aby schemat zgadzał się z tym dołączonym do źródeł Protein. Jeszcze się zastanawiam czy dioda BAT83 i tranzystor BC557 też są odpowiednie. Taki programator w razie uszkodzenia bardzo prosto naprawić - nie ma na pokładzie niczego co trzeba programować.

Kilos: zerknąłem na ten schemat i to jest żywcem ZL4PRG w standardzie DLC5 do Xilinx który mam z tą różnicą że tutaj TDO idzie via ACK (10), a u mnie z SELECT-u (13), po małej modyfikacji powinien podejść pod Lattice

Kupiłem programator ZL4PRG - będę ciąć kilka ścieżek, parę połączeń trzeba będzie dorobić, wymienić kilka rezystorów i kondensatorów aby schemat zgadzał się z tym dołączonym do źródeł Protein. Jeszcze się zastanawiam czy dioda BAT83 i tranzystor BC557 też są odpowiednie. Taki programator w razie uszkodzenia bardzo prosto naprawić - nie ma na pokładzie niczego co trzeba programować.

24.09.2017 17:33

[#769]

Re: Protein turbo A500

@Adinfo, post #768

Przerobiłem programator ZL4PRG v2 pod Lattice, niestety ispLEVER mi go nie wykrywa w porcie LPT. Przeanalizowałem schematy i mam to zrobione tak jak programator ze źródeł Protein. Jakiego oprogramowania można jeszcze użyć zamiast ispLEVER. Nie przechodzi testu power mimo podłączonego zasilania. Nie wiem w sumie czy ten programator ma zachowywać się tak samo jak ZL11PRG v2. Nie podłączałem programatora pod Protein tylko do portu LPT i do zasilania.

24.09.2017 18:06

[#771]

Re: Protein turbo A500

@Jenot, post #770

Czyli to że ispLEVER mi go nie wykrywa może być naturalne? Schemat mam prawie identyczny z

(za wyjątkiem rezystorów 470R, których nie mam, dodatkowo pin 11 i 13 układu nie jest nigdzie podpięty - tak jak na schemacie do kabla z Protein, mam zdjęty mostek między pinami LPT 8 i 12).

Ostatnia aktualizacja: 24.09.2017 18:07:35 przez Adinfo

(za wyjątkiem rezystorów 470R, których nie mam, dodatkowo pin 11 i 13 układu nie jest nigdzie podpięty - tak jak na schemacie do kabla z Protein, mam zdjęty mostek między pinami LPT 8 i 12).

Ostatnia aktualizacja: 24.09.2017 18:07:35 przez Adinfo

24.09.2017 18:09

[#772]

Re: Protein turbo A500

@Adinfo, post #771

Ja nie wiem, nie używałem programatora Lattice na LPT. U mnie nie chciał się zainstalować sterownik z ispLever Classic na Win10 (dla programatora LPT też powinieneś chyba zainstalować sterownik). Dlatego ściągnąłem Standalone Programmer, zainstalowałem, przy pierwszym uruchomieniu zapytał o instalację sterowników, potem programator był widziany przez Standalone Programmer, Diamond i ispLever Classic.

Ostatnia aktualizacja: 24.09.2017 18:09:49 przez Jenot

Ostatnia aktualizacja: 24.09.2017 18:09:49 przez Jenot

24.09.2017 18:20

[#773]

Re: Protein turbo A500

@Jenot, post #772

Próbuję pobrać Programmer Standalone 3.9 32-bit for Windows po zalogowaniu na stronie Lattice ale nic się nie pobiera. Wersja 64-bit to samo. Jest opcja "pobierz zaznaczone jak ZIP" - po naciśnięciu przeładowuje stronę i tak zostaje.

Ostatnia aktualizacja: 24.09.2017 18:22:25 przez Adinfo

Ostatnia aktualizacja: 24.09.2017 18:22:25 przez Adinfo

24.09.2017 21:00

[#780]

Re: Protein turbo A500

@Adinfo, post #779

Kolejne testy z zasilaniem, niestety nic. Podłączyłem Protein pod zasilanie (bez programatora) - jeden mach grzał się mocno - fabrycznie uwalony - od razu sprawdzam jak podłączam bo różnie może być. Możliwe jeszcze, że wtedy co upaliło ZL11PRG v2 poleciał też częściowo port LPT, tego wprost nie widać a może to jest przyczyna, że mi programatora nie wykrywa. Protein z machami też niczego nie zmienia z wykrywaniem kabla. Mam starego kompa z Win95 i LPT, tylko czy ispLEVER na tym ruszy, wątpię.